Technical Areas

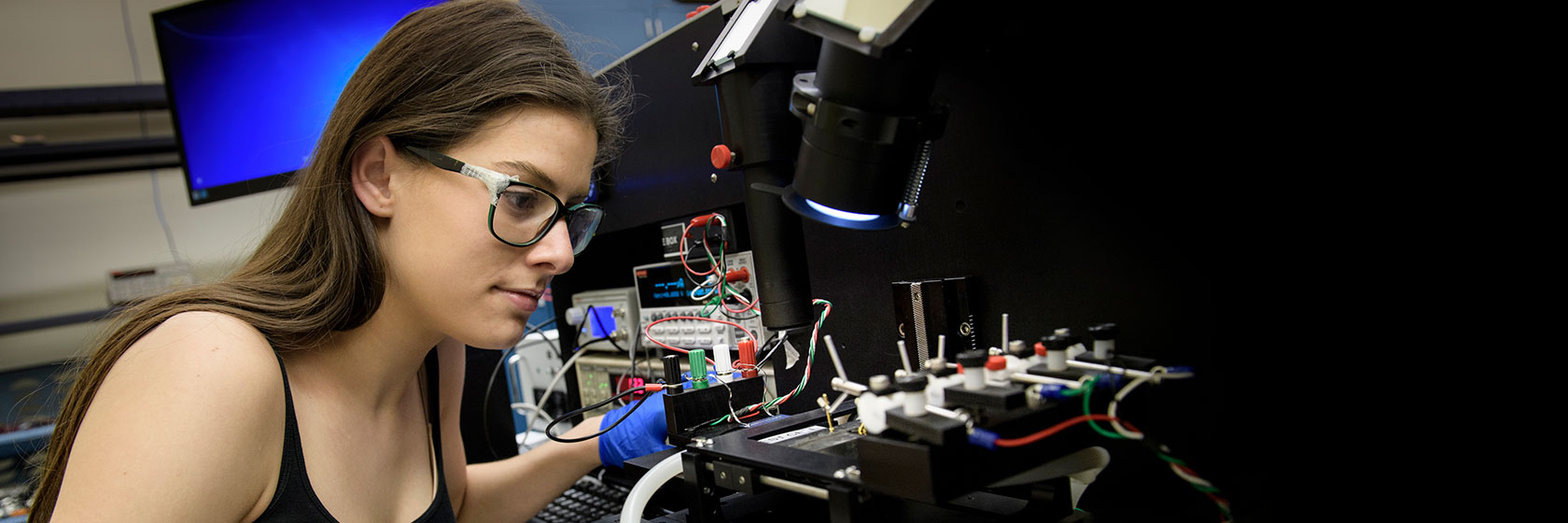

SCALE students gain expertise and hands-on experience with current and future technology demands, ensuring U.S. prowess in building the domestic semiconductor industrial base and the critical infrastructure and national defense applications it supports.

Background

Radiation in natural and manmade environments can greatly affect the operation and long-term performance of microelectronics. Radiation hardening is making electronic components and circuits resistant to damage or malfunction caused by high levels of ionizing radiation. Transient effects include single-event effects like memory bit flips; permanent effects include single-event latchups that prevent individual devices from operating. Mitigation approaches include radiation-hardening by process and radiation-hardening by design.

Curriculum

Courses include:

- Senior design projects

- Dual-level RH special topics

Background

The Access to Radio Frequency & Opto-electronics (RF/OE) Microelectronics Technical Execution Area is one of six technology-focused components of the Trusted and Assured Microelectronics (T&AM) Program, which drives modernization of defense systems through access to advanced microelectronics technologies that leverage state-of-the-art (SOTA), commercially driven capabilities. The RF/OE program works to ensure access to domestic manufacturing of next-generation devices, while also developing cutting-edge and cost-saving technologies to deploy on a variety of defense platforms. The RF/OE Technical Execution Area supports two main strategic goals. First, to access, mature, and assure SOTA manufacturing capabilities for RF Gallium Nitride (GaN) and Photonic Integrated Circuits. This directly enables domestic manufacturing of next generation sensors and communication devices. Second, RF/OE develops, demonstrates, and transitions SOTA devices and intellectual property via rapid prototyping, driving affordable innovation for the Defense Industrial Base.

Background

Moore’s law has led to an exponential increase in the number of devices that can fit onto a single chip. This has led to a new era where most electronic systems contain chips that integrate various (hitherto discrete) components such as microprocessor, DSPs, dedicated hardware processing engines, memories, and interfaces to I/O devices and off-chip storage. Most electronic systems today—cell phones, iPods, set-top boxes, digital TVs, automobiles—contain at least one such System-on-chip (SoC). Designing SoCs is a highly complex process. Before entering the traditional VLSI implementation process (RTL, logic & physical design), designers must perform the challenging tasks of developing a functional specification, partitioning and mapping of functions onto hardware components and software, developing a communication architecture to interconnect the components, functional/performance/power analysis and validation, and more.

Curriculum

Courses include:

- Vertically Integrated Projects

- Dual-level SoC special topics

Background

The rapid increase in chip performance associated with Moore’s law has also raised interest and expectations around creating packaging devices with improved size, weight, and power. To keep sizes manageable while improving functionality, complex packaged electronics like iPhones require similar components to be compressed together horizontally and vertically, and combined with dissimilar components providing complementary functions. Significant challenges in heterogeneous integration include maintain reliability of connections such as solder bumps, managing thermal cycling, and limiting damage from mechanical stress that can cause failures.

Curriculum

Courses include:

- Senior design projects

- Dual-level HI/AP cross-cutting topics

Background

Artificial intelligence (AI) provides a tremendous amount of sophisticated information analysis and decision-making capabilities. AI has even been characterized as a potential third offset for DOD. It plays an increasingly central role in operations, but hard problems relating to trust, verifiability, risk modeling, bias, fairness, human interaction, and feedback remain.

This area aims to characterize, investigate, and manage these challenges with a suite of toolboxes developed through student research projects across multiple universities in the SCALE consortium.

Major Project Areas:

- Human-machine Pairing for Trustworthy AI

- Statistical Analysis and Measurement of Neural Networks

- Knowledge Representation and Engineering

- Trust and Verifiability in AI

- Framework Infrastructure Development

- 24/7 AI Career Cyber-Coaching for U.S. Workers